2026-05-13

菲利华提到公司石英电子布项目仍处于客户端小批量测试及终端客户的认证阶段。

2026-05-13

为深度聚焦新一代高端FPGA与PSoC、人工智能和新一代存储技术三大核心方向,拟成立集成电路工程技术融合创新中心。

2026-05-13

研究团队构建了“AI决策+自动化合成”的闭环研发体系,实现了高纯度、高一致性、高效率的KrF光刻胶树脂创制。

2026-05-12

媒体报道称,SK海力士正在考虑采用英特尔研发的2.5D封装技术“嵌入式多芯片互连桥接(EMIB)”

2026-05-13

此次试验中使用的太阳能发电装置功率较低,为44千瓦,但若将其与未来预计增加的海上风电相结合,便有望建成大型数据中心。

2026-05-12

据OpenAI介绍,新公司名为OpenAI Deployment Company,主要目标是将专注于前沿AI落地的工程师嵌入企业内部,与各团队紧密合作,识别AI能够带来最大效益的业务环节。

2026-05-12

知名博主@手机芯片达人 透露,埃隆·马斯克旗下的特斯拉正面临来自美国政府的压力,要求将其下一代AI6.5芯片的代工订单从台积电转移至英特尔。

2026-05-12

软银集团于周一宣布,将在大阪府夏普原堺工厂厂区内研发、生产电芯及电池储能系统,软银也正在该地块建设大型人工智能数据中心园区。

2026-05-13

为应对全球汽车行业的下行趋势,奥托立夫将逐步缩减其在土耳其的制造业务,并计划于2028年全面停产。

2026-05-12

截至2026年5月,松下新能源公司4680规格车用圆柱锂离子电池仍未获客户最终批准,无法进入量产阶段。

2026-05-12

新工厂将落户于马哈拉施特拉邦的比德金(Bidkin)工业区,投产初期计划雇用约2800名员工,以当地招聘为主,覆盖冲压、焊接、喷涂及组装等完整工序。

2026-05-12

该合资公司将通过其位于日本横滨的开发销售子公司EMT,推出一个面向日本市场的自有品牌纯电动汽车。

2026-05-13

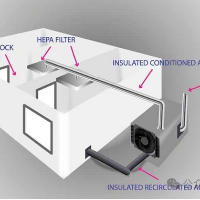

整体工程已从初步定型阶段稳步迈入全面竣工阶段,厂房建设严格按照设计标准推进,车间内部装修进入收尾。

2026-05-12

苏州市贝特利高分子材料股份有限公司首次公开发行股票申请已获通过,拟在深交所创业板挂牌上市。

2026-05-12

SEG Solar宣布将在得克萨斯州休斯顿新建一座4GW组件工厂,新工厂占地面积近50万平方英尺,投资额超过2亿美元,预计将创造多达800个本地就业岗位。

2026-05-12

项目直流侧总装机124.72472MWp,交流侧总装机100MW,光伏区共设置26个子方阵,计划安装715Wp和610Wp两种规格的单晶硅光伏组件。

王兆龙 | 2026-01-22

夜晚的光纤世界,总有一些肉眼看不见的信号在闪烁。它们以光速穿行,从海底电缆到数据中心,再到你的手机屏幕,每一次“点赞”和“推送”背后,都是亿万次光的跃迁。而在这场无声的速度竞赛中,有一种材料正在悄悄成为主角——薄膜铌酸锂(Lithium Niobate on Insulator,LNOI)。

大半导体产业网 | 2026-04-29

今天,随着信道探测(Channel Sounding)、Auracast™广播音频、高吞吐量数据传输(HDT) 等新一代规范的落地与推进,蓝牙正在重新定义无线技术的边界。

大半导体产业网 | 2026-05-12

2026年3月13日,《中华人民共和国国民经济和社会发展第十五个五年规划纲要》正式发布,集成电路被置于新兴支柱产业之首。

奥芯明 | 2026-04-13

奥芯明首席执行官许志伟深入分享了奥芯明如何凭借“本土创新+全球引领”的双重基因深耕中国市场,并深度解析了AI对半导体设备行业带来的双向重塑与人才体系变革,助力中国客户在这场智能革命中抢占先机。

为方便SEMI中国ECS精英客户阅读SEMI China每日要闻,自2024年12月20日起,订户登陆阅读即可及时掌握全球产业大事。登陆密码:您申请时填写的完整邮箱地址!